Was bedeutet "für die Prüfung konzipiert"?

Designed for Testing (DFT) besteht aus einer Reihe von Entwurfstechniken, die einem Leiterplattenentwurf Testfunktionen hinzufügen. Diese zusätzlichen Funktionen zielen darauf ab, das Testen von (bestückten) Leiterplatten zu vereinfachen und somit die Kosten für das Testen zu senken, was zu einer Reduzierung der Kosten führen kann:

- Die für die Prüfung aufgewendete Zeit

- Die mit der Erzeugung der Testvektoren verbundenen Kosten

- Die Anzahl der Entwurfsiterationen, die erforderlich sind, um eine akzeptable Testabdeckung oder -ausbeute zu erreichen.

Der Zweck von Designed for Testing (DFT)

Mit der Prüfung soll sichergestellt werden, dass die bestückte Leiterplatte keine Herstellungsfehler aufweist, die den ordnungsgemäßen Betrieb des Produkts beeinträchtigen könnten.

Tests können in verschiedenen Phasen des Produktionsprozesses durchgeführt werden und bei bestimmten Produkten auch für die Wartung der Hardware in der Umgebung des Kunden genutzt werden. Die Tests werden im Allgemeinen durch Testprogramme gesteuert, die mit Hilfe von automatischen Testgeräten (ATE) oder, im Falle der Systemwartung, innerhalb des montierten Systems selbst durchgeführt werden. Neben dem Auffinden und Anzeigen von Fehlern (d. h. der Test schlägt fehl) können Tests potenziell auch Diagnoseinformationen über die Art der gefundenen Anomalien aufzeichnen. Die Diagnoseinformationen können verwendet werden, um die Ursache des Fehlers zu ermitteln.

Mit anderen Worten: Die Reaktion von Vektoren (Mustern) einer guten Schaltung wird mit der Reaktion von Vektoren (mit denselben Mustern) eines DUT (zu prüfendes Gerät) verglichen. Wenn die Reaktion gleich ist oder übereinstimmt, ist die Schaltung gut. Andernfalls ist die Schaltung nicht wie vorgesehen hergestellt worden.

DFT spielt eine wichtige Rolle bei der Entwicklung von Testprogrammen und als Schnittstelle für Testanwendung und Diagnose. Die automatische Generierung von Testmustern, oder ATPG, ist viel einfacher, wenn die richtigen DFT-Regeln und Vorschläge implementiert sind.

Einige Techniken sind sehr einfach, wie z. B. das Zurücksetzen eines Entwurfs. Ohne diese Rücksetzungen müssen die Testvektoren eine Referenzierungssequenz durchführen, die einen Entwurf in einen bekannten Zustand versetzt, damit die Prüfung überhaupt beginnen kann.

Typischer ist die Einführung von scanbasierten Tests, eingebauten Selbsttests (BIST) oder verbesserter Beobachtbarkeit mit JTAG. Die meisten Testschaltungen werden nach der Synthese eingeführt, obwohl BIST-Techniken oft in die Funktionalität des Blocks integriert sind. Eine frühzeitige Analyse kann während der RTL-Designphase durchgeführt werden, um Designentscheidungen zu ermitteln, die sich auf die Testbarkeit des Designs auswirken können.

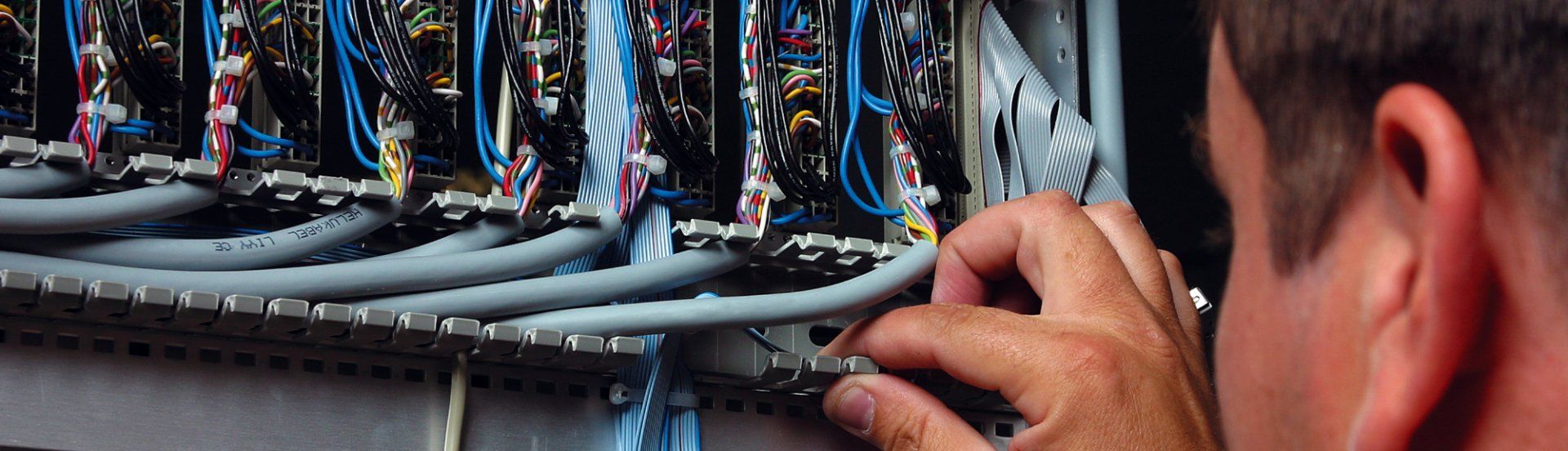

Konzipiert für Tests bei Confed

Unsere Spezialisten in den verschiedenen Fachbereichen verfügen über umfangreiche Erfahrungen und Kenntnisse in der Konzeption, Entwicklung und Prüfung von Produkten. Sie stehen Ihnen jederzeit mit Rat und Tat zur Seite.

Für Confed ist es wichtig, Qualitätsprodukte ohne Herstellungsfehler oder -mängel zu liefern. Deshalb ist es wichtig, die Produkte vor der Übergabe an das Montageteam oder den Benutzer zu testen.

Möchten Sie mehr über Designed for Testing bei Confed erfahren und welche Möglichkeiten Sie haben? Nehmen Sie Kontakt mit uns auf. Wir beantworten gerne Ihre Fragen und denken mit Ihnen über Lösungen nach.

Wählen Sie Confed. Entscheiden Sie sich für Schnelligkeit, Zuverlässigkeit und Qualität.

Neugierig?

Sind Sie neugierig geworden, was wir in diesem Bereich für Sie tun können? Wir möchten Sie einladen, mit uns Kontakt aufzunehmen. Sie können dies einfach telefonisch oder über unsere allgemeine E-Mail-Adresse tun. Sie können uns auch eine Anfrage über die Kontaktseite schicken und wir werden uns so schnell wie möglich bei Ihnen melden.

Kontaktieren Sie uns unter:

info@confed.eu oder Tel.: +31(0) 33 454 1340